一个4位计数器程序在ISE 联合modelsim进行仿真,代码如下

testbench的内容:

module count4_tb;

reg clk,reset;

wire [3:0] out;

parameter DELY=100;

count4 mycount(out,reset,clk);

always #(DELY/2) clk=~clk;

initial begin

clk=0;

reset=0;

#DELY reset=1;

#DELY reset=0;

#(DELY*200) $finish;

end

initial $monitor($time,,,"clk=%d reset=%d out=%d",clk,reset,out);

endmodule

count4.v的内容:

module count4(out,reset,clk

);

output [3:0] out;

input reset,clk;

reg [3:0] out;

always@(posedge clk) begin

if(reset)

out<=0;

else

out<=out+1;

end

endmodule

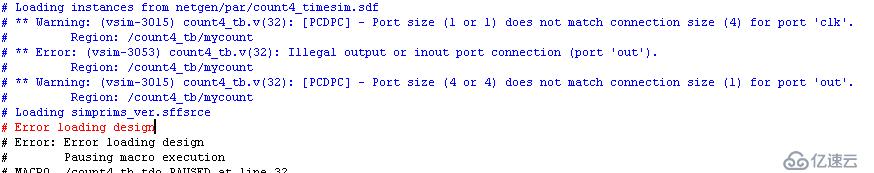

功能仿真,没有错误,而布局布线后仿真,有如下错误提示

改正办法:

将testbench 中的 count4 mycount(out,reset,clk);改为count4 mycount(.out(out),.reset(reset),.clk(clk));时序仿真就会正确运行。

亿速云「云服务器」,即开即用、新一代英特尔至强铂金CPU、三副本存储NVMe SSD云盘,价格低至29元/月。点击查看>>

免责声明:本站发布的内容(图片、视频和文字)以原创、转载和分享为主,文章观点不代表本网站立场,如果涉及侵权请联系站长邮箱:is@yisu.com进行举报,并提供相关证据,一经查实,将立刻删除涉嫌侵权内容。