米尔科技推出的MYD-CZU3EG开发板搭载的就是UltraScale+ MPSoC平台器件 — XCZU3EG,它集成了四核Cortex-A53 处理器,双核 Cortex-R5 实时处理单元以及Mali-400 MP2 图形处理单元及 16nm FinFET+ 可编程逻辑相结合的异构处理系统,具有高性能,低功耗,高扩展等特性,除了这款异构SOC之外,板子还搭载了丰富的接口和完善的开发资料,下面我们来一探究竟。

开箱

暖色调的简洁外包装上印有一行“Make Your idea Real”。

开箱之后就是摆放在内衬中的板卡和配套设备。除了板卡之外,配套的电源、数据线、SD卡和光盘等等,可谓考虑齐全。

板卡资源介绍

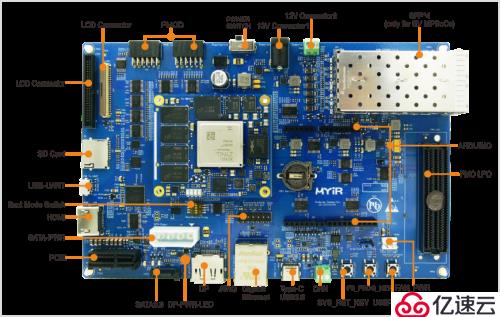

笔者迫不及待的拆开板卡的防静电袋。MYD-CZU3EG 开发板由MYC-CZU3EG 核心板加MYB-CZU3EG 底板组成。散热器下面是核心板,这是一个CPU最小系统模块,集成了主处理器和存储。底板是一块外设接口板,集成了电源和多种接口,方便评估或集成。

下面我们详细的了解一下板卡详细的组成结构,首先,核心板基于Xilinx XCZU3EG全可编程处理器,4核Cortex-A53(Up to 1.5GHZ)+FPGA(154K LE),具体型号:XCZU3EG-1SFVC784,(未来可选配XCZU2CG, XCZU3CG,XCZU4EV,XCZU5EV),性能强大;板载4GB DDR4 SDRAM(64bit,2400MHZ) 及丰富的存储资源,从容应对复杂运算;板载千兆以太网PHY 和USB PHY , 轻松实现高速互联,如此奢华的配置,板子尺寸只有62*50mm,令人赞叹。

另外,板子选材和用料讲究,据称使用了Intel电源模块,松下的M6 PCB板材,Micron存储,村田电容,还是非常良心的。

底板的外设接口丰富,板载了串口,网口,HDMI,DP,SATA,PCIE,USB3.0 Type-C,LCD,PMOD,Arduino,FMC-LPC,TF 卡接口,SFP,ADC,CAN等多种接口,方便用户评估或集成。这些接口根据SOC的结构,有的接在PS端,有的接在PL端。

PS 单元:

Zynq UltraScale+ MPSoC介绍

1.真正的全可编程异构多处理SOC

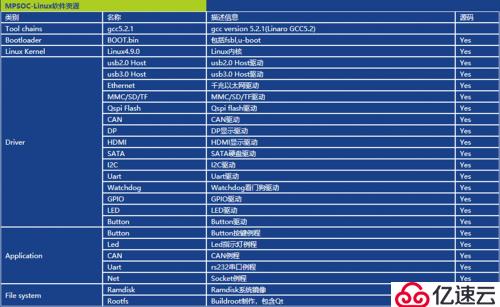

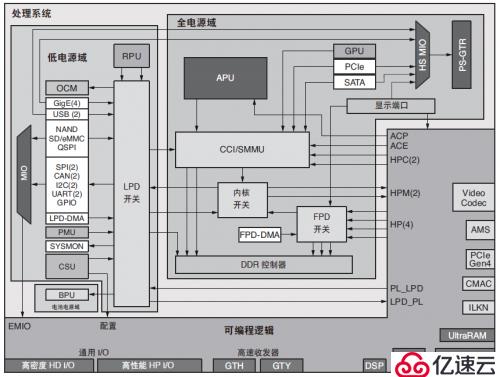

在使用板子之前,我们先来了解一下这款板卡的核心芯片——XCZU3EG,这是Xilinx继ZYNQ-7000系列之后推出的真正的全可编程异构平台,Zynq® UltraScale+ MPSoC 器件不仅提供 64 位处理器可扩展性,同时还将实时控制与软硬件引擎相结合,支持图形、视频、波形与数据包处理。置于包含通用实时处理器和可编程逻辑的平台上,三个不同变体包括双应用处理器 (CG) 器件、四核应用处理器和 GPU (EG) 器件、以及视频编解码器 (EV) 器件, 为 5G 无线、下一代 ADAS 和工业物联网创造了无限可能性。

MYD-CZU3EG开发套件目前搭载的是EG,后期还可以选配CG或EV器件。EG 器件采用运行速率高达 1.5GHz 的四核 ARM® Cortex-A53 平台与双核 Cortex-R5 实时处理器、Mali-400 MP2 图形处理单元及 16nm FinFET+ 可编程逻辑相结合。

该开发板有着无与伦比的集成度、高性能和低功耗特点,与 Zynq-7000 SoC 相比,系统级性能功耗比提升5 倍,为交付最低系统功耗而精心设计,官方给出的典型应用包括基带 L1 加速、公共安全与移动无线电和8x8 100 MHz TD-LTE 远端射频单元等场景。

说到应用,不得不提Zynq UltraScale+ MPSoC最最擅长的领域——面向视频编解码器和图形引擎的前沿多媒体解决方案。赛灵思SoC为多媒体解决方案提供了多种支持,包括:

EV 器件带有集成型 GPU 和H.264 / H.265视频编解码器,专为超高清 (UHD) 视频而设计带有集成型 H.264 / H.265 视频编解码器,能够同时编解码达 4Kx2K (60fps) 的视频,可实现单芯片4K视频处理,当然MYD-CZU3EG开发板使用的是EG器件,没有视频编解码器,但是有Mali-400 MP2 GPU。

Mali-400 MP2 GPU与 APU 直接绑定,还可在帧缓存中加速视频图形渲染,从而实现显示器输出。GPU 可通过独立的并行引擎进行像素渲染,速度远高于依靠 CPU 来处理图形,而且与需要设计人员添加片外 GPU 引擎的解决方案相比,成本与功耗均更低。GPU 通过全面可编程的架构加速 2D 和 3D 图形,该架构既支持基于着色器的图形 API ,也支持固定功能图形 API 。GPU 具有抗锯齿功能,能实现最佳图像质量,且几乎不会造成额外的性能损耗。Xilinx配套提供经实践检验的全套 Linux 驱动程序,能自动将图形命令从 APU 转到 CPU 处理。

另外,Zynq UltraScale+ MPSoC 提供高速互联外设,后者包含集成式 DisplayPort 接口模块。DisplayPort接口位于 PS 端,可多路复用至四个专用高速串行收发器中的两个,工作速率高达 6 Gb/s。该架构摆脱了对于额外显示芯片的需求,进一步降低了系统 BOM 成本。

DisplayPort 接口基于 VESA DisplayPort Standard Version 1 和 Revision 2a 开发,其提供的多个接口能处理来自 PS 或 PL 的实时音视频流,也能存储来自存储器帧缓存的音视频。它同时支持两个音视频流水线,支持 alpha 混合、chroma 复采样、色彩空间转换和音频混合等功能的动态渲染。DisplayPort 既可使用一个 PS PLL,也能使用 PL 的时钟生成像素时钟。

除视频编解码器和图形处理之外,多媒体应用还需要其他重要组件,如视频数据的输入输出管理 , 以及处理高速视频数据的功能。在 PL 内可设计定制化逻辑,用于捕获来自直播源的视频。例如,SDI RX、HDMI RX、MIPI CSI IP 等协议均可用于捕获不同来源的原始视频。视觉算法可用于采集来自原始数据的重要信息,如路标识别和针对驾驶员辅助技术的动作检测、视频监控面部识别、高级拍摄应用的物体与动作识别等。除收集数据外,算法还可用于音视频广播和视频会议等用例中处理与操控原始数据。考虑到今后几年视频分辨率不可避免的攀升态势,有关算法需要具备极高的工作速度。PL 为此类算法提供了所需的硬件加速功能,便于大幅提高性能,满足下一代技术需求。

Zynq UltraScale+ MPSoC 的灵活性能加速计算密集型应用程序,在 GPU、CPU 和 PL 之间共享工作负载,在 PL 中可卸载复杂的算数计算以实现硬件加速,并且在 APU 上可预先计算 OpenGL 着色语言 (GLSL) 一致变量。GPU 着色器核心上的计算仅适用于顶点和片断之间不同的值。整批顶点中所有保持常量的值在 CPU 上处理最为有效。

Zynq UltraScale+ MPSoC 在设计之初就考虑了高效电源管理问题,该器件被分为四个电源域:

Zynq UltraScale+ MPSoC 含有可控制电源域的创新型平台管理单元 (PMU),。PMU 负责器件的安全管理,并监管电源域内的电源。不用的电源域可在启动时关闭,然后智能地通过中断或事件唤醒,实现精细的电源管理。

我们已经知道Zynq UltraScale+ MPSoC 内部分了多个处理核心,四核ARM Cortex-A53是应用处理单元,具有高效的基线性能,适合Linux应用处理;双核 ARM Cortex-R5是实时处理单元理想适用于低时延确定性应用,诸如安全模块和 APU 任务分担等,另外图形引擎,高速外设等针对特定应用做了优化,各个模块各司其职,系统性能明显提升。该器件采用了台积电 (TSMC) 的 16nm FinFET 工艺节点,。该工艺节点采用更高效的晶体管实现方案,具备最佳的开关速度以及比平面工艺更低的漏电流,因此能实现更高性能和更低功耗。从 28nm 的 Zynq-7000 到 16nm 的 Zynq UltraScale+ MPSoC,性能提升了 60%,功耗降低 20%,使原始处理器性能提升 2.7 倍。

示例

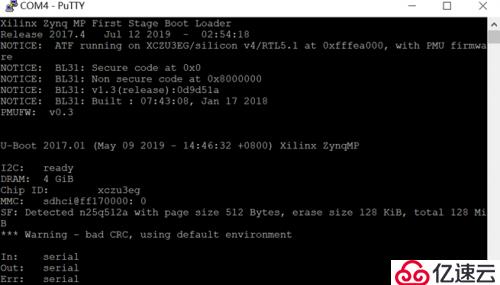

板子QSPI闪存预先烧录了Linux镜像,默认也是从QSPI闪存启动的,使用数据线连接板子串口和PC,连接电源,板子上电,打开putty,可以看到系统启动信息。通过命令行可以登录,默认密码是root。

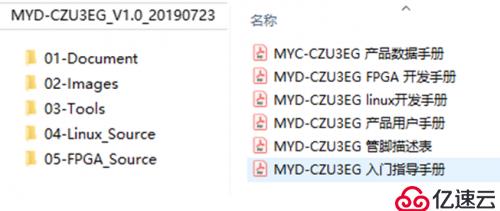

光盘中也提供了系统的镜像文件,用户如果不熟悉Linux系统编译,可以直接使用。

另外,MYD-CZU3EG 光盘中提供了常用外设的演示程序,例如:

这里我们使用Xilinx Vivado新建一个HelloWorld工程,生成启动镜像,从TF卡启动。整个过程分为:

免责声明:本站发布的内容(图片、视频和文字)以原创、转载和分享为主,文章观点不代表本网站立场,如果涉及侵权请联系站长邮箱:is@yisu.com进行举报,并提供相关证据,一经查实,将立刻删除涉嫌侵权内容。