жӮЁеҘҪпјҢзҷ»еҪ•еҗҺжүҚиғҪдёӢи®ўеҚ•е“ҰпјҒ

жӮЁеҘҪпјҢзҷ»еҪ•еҗҺжүҚиғҪдёӢи®ўеҚ•е“ҰпјҒ

жң¬зҜҮж–Үз« з»ҷеӨ§е®¶еҲҶдә«зҡ„жҳҜжңүе…іжҖҺд№ҲиҝӣиЎҢIICеҚҸи®®зҡ„FPGAе®һзҺ°пјҢе°Ҹзј–и§үеҫ—жҢәе®һз”Ёзҡ„пјҢеӣ жӯӨеҲҶдә«з»ҷеӨ§е®¶еӯҰд№ пјҢеёҢжңӣеӨ§е®¶йҳ…иҜ»е®ҢиҝҷзҜҮж–Үз« еҗҺеҸҜд»ҘжңүжүҖ收иҺ·пјҢиҜқдёҚеӨҡиҜҙпјҢи·ҹзқҖе°Ҹзј–дёҖиө·жқҘзңӢзңӢеҗ§гҖӮ

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғеӣҫ1 13 IICжЁЎеқ—зҡ„е»әжЁЎеӣҫ

вҖғвҖғеӣҫ1 13жҳҜ IIC еӮЁеӯҳжЁЎеқ—зҡ„е»әжЁЎеӣҫпјҢе·Ұиҫ№жҳҜйЎ¶еұӮдҝЎеҸ·пјҢеҸіиҫ№еҲҷжҳҜжІҹйҖҡз”Ёзҡ„й—®зӯ”дҝЎеҸ·пјҢеҶҷе…Ҙең°еқҖ iAddrпјҢеҶҷе…Ҙж•°жҚ® iDataпјҢиҝҳжңүиҜ»еҮәж•°жҚ® oDataгҖӮCall/Done жңүдёӨдҪҚпјҢеҚіиЎЁзӨәиҜҘжЁЎеқ—жңүиҜ»еҠҹиғҪиҝҳжңүдәӣеҠҹиғҪгҖӮе…·дҪ“еҶ…е®№пјҢжҲ‘们иҝҳжҳҜжқҘзңӢд»Јз Ғеҗ§пјҡ

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғд»Јз Ғ2 1 IICд»Јз ҒеЈ°жҳҺ

1. parameter FCLK = 10'd125, FHALF = 10'd62, FQUARTER = 10'd31;

2. parameter THIGH = 10'd30, TLOW = 10'd65, TR = 10'd15, TF = 10'd15;

3. parameter THD_STA = 10'd30, TSU_STA = 10'd30, TSU_STO = 10'd30;

вҖғвҖғеҰӮд»Јз Ғ2 1 жүҖзӨәпјҢ FCLK иЎЁзӨә 400Khz зҡ„е‘ЁжңҹпјҢ FHALF иЎЁзӨә 1/2 е‘ЁжңҹпјҢ FQUARTER иЎЁзӨә 1/4 е‘ЁжңҹгҖӮ

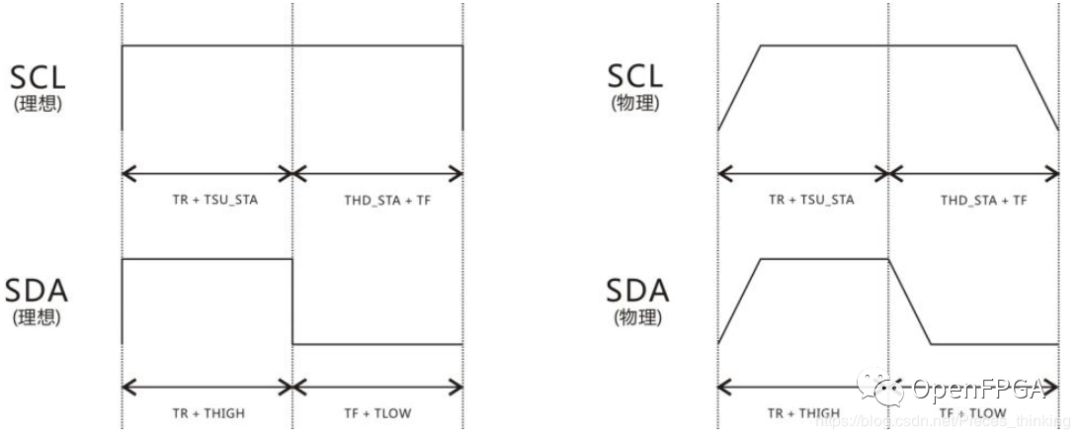

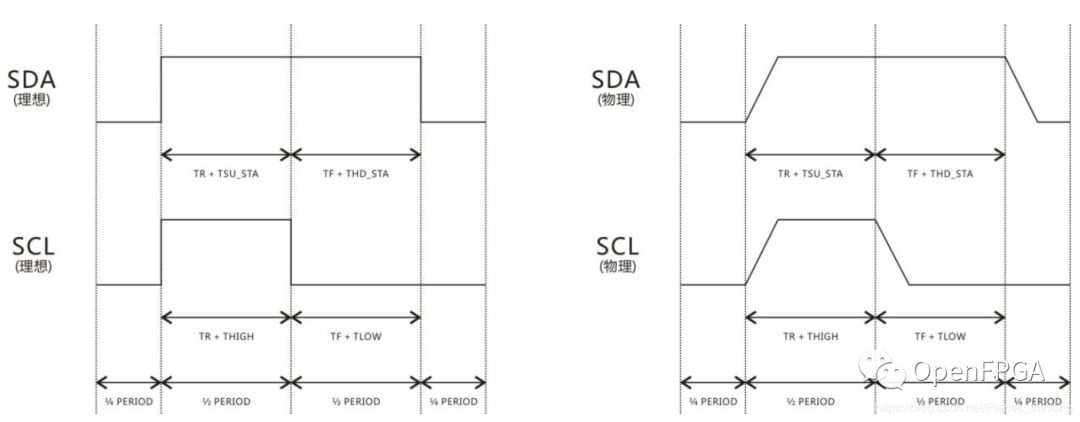

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғеӣҫ2 14 иө·е§ӢдҪҚ

вҖғвҖғйҰ–е…Ҳи®©жҲ‘们е…Ҳзһ§зһ§иө·е§ӢдҪҚиҝҷжһҡжӢјеӣҫгҖӮеҰӮеӣҫ2 14жүҖзӨәпјҢе·ҰеӣҫжҳҜиө·е§ӢдҪҚзҡ„зҗҶжғіж—¶еәҸпјҢеҸіеӣҫжҳҜиө·е§ӢдҪҚзҡ„зү©зҗҶж—¶еәҸгҖӮIIC жҖ»зәҝзҡ„иө·е§ӢдҪҚд№ҹе°ұзұ»дјјдёІеҸЈжҲ–иҖ… PS/2 зӯүдј иҫ“еҚҸи®®зҡ„иө·е§ӢдҪҚпјҢ然иҖҢдёҚеҗҢзҡ„жҳҜпјҢ IIC жҖ»зәҝзҡ„иө·е§ӢдҪҚжҳҜ SCL жӢүй«ҳ TR + TSU_STA + THD_STA + TF д№Ӣд№…пјҢжҚўд№Ӣ SDA еҲҷжҳҜжӢүй«ҳ TR + THIGH 然еҗҺжӢүдҪҺ TF + TLOWгҖӮиө·е§ӢдҪҚжҖ»е’ҢжүҖз”ЁжҺүзҡ„ж—¶й—ҙпјҢжҒ°жҒ°еҘҪжңүдёҖдёӘйҖҹзҺҮзҡ„е‘ЁжңҹгҖӮеҜ№жӯӨпјҢ Verilog еҲҷеҸҜд»Ҙиҝҷж ·жҸҸиҝ°пјҢз»“жһңеҰӮдёӢжүҖзӨә:

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғд»Јз Ғ2 2 IICиө·е§ӢдҪҚдә§з”ҹд»Јз Ғ

1. begin

2. isQ = 1;

3. rSCL <= 1'b1;

4. if( C1 == 0 ) rSDA <= 1'b1;

5. else if( C1 == (TR + THIGH) ) rSDA <= 1'b0;

6. if( C1 == (FCLK) -1) begin C1 <= 10'd0; i <= i + 1'b1; end

7. else C1 <= C1 + 1'b1;

8. end

вҖғвҖғеҰӮд»Јз Ғ2 2жүҖзӨәпјҢ第 2 иЎҢзҡ„ isQ = 1 иЎЁзӨәи®ҫзҪ® SDA дёәиҫ“еҮәзҠ¶жҖҒпјҲеҚіж—¶з»“жһңпјүпјҢ第 3 иЎҢеҲҷиЎЁзӨә SCL дёҖзӣҙжҢҒз»ӯжӢүй«ҳзҠ¶жҖҒпјҢ第 4~5 иЎҢиЎЁзӨә C1 дёә 0 зҡ„ж—¶еҖҷ SDA жӢүй«ҳпјҢзӣҙеҲ° C1 дёәTR+THIGH жүҚжӢүдҪҺ SDAгҖӮ第 6~7 иЎҢиЎЁзӨәдёҖдёӘжӯҘйӘӨжүҖйҖ—з•ҷзҡ„ж—¶й—ҙгҖӮ

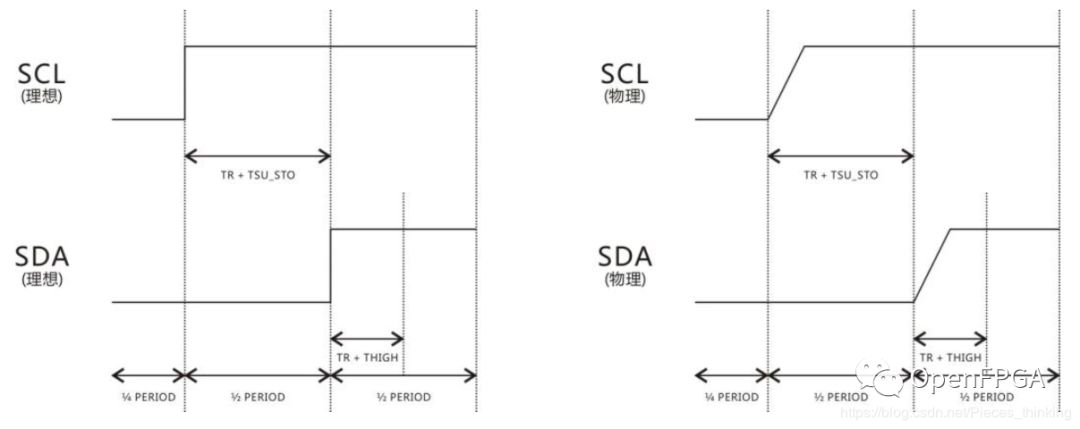

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғеӣҫ3 15 з»“жқҹдҪҚ

вҖғвҖғеӣҫ3 15жҳҜз»“жқҹдҪҚзҡ„ж—¶еәҸеӣҫпјҢ IIC и®ҫеӨҮзҡ„ж“ҚдҪңеҘҪеқҸдёҖиҲ¬йғҪеҸ–еҶіз»“жқҹдҪҚгҖӮдҝқйҷ©иө·и§ҒпјҢ SCL дёҺSDA йғҪдәӢе…ҲжӢүдҪҺ 1/4 е‘ЁжңҹпјҢзҙ§жҺҘзқҖ SCL дјҡжӢүй«ҳ TR+TSU_STOпјҲжҲ–иҖ… 1/2 е‘ЁжңҹпјүпјҢжңҖеҗҺеҸҲдҝқжҢҒй«ҳз”өе№і 1/2 е‘ЁжңҹгҖӮеҸҚд№ӢпјҢ SDA дјҡжӢүдҪҺ 1/2 е‘ЁжңҹпјҢйҡҸд№ӢжӢүй«ҳ TR+THIGHпјҲжҲ–иҖ… 1/2е‘ЁжңҹпјүгҖӮеҜ№жӯӨпјҢ Verilog еҸҜд»Ҙиҝҷж ·иЎЁзӨәпјҢз»“жһңеҰӮд»Јз Ғ2 3жүҖзӨәпјҡ

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғд»Јз Ғ2 3 IICз»“жқҹдҪҚд»Јз Ғе®һзҺ°

1. begin

2. isQ = 1'b1;

3.

4. if( C1 == 0 ) rSCL <= 1'b0;

5. else if( C1 == FQUARTER ) rSCL <= 1'b1;

6.

7. if( C1 == 0 ) rSDA <= 1'b0;

8. else if( C1 == (FQUARTER + TR + TSU_STO ) ) rSDA <= 1'b1;

9.

10. if( C1 == (FQUARTER + FCLK) -1 ) begin C1 <= 10'd0; i <= i + 1'b1; end

11. else C1 <= C1 + 1'b1;

12. end

вҖғвҖғеҰӮд»Јз Ғ2 3жүҖзӨәпјҢ第 2 иЎҢиЎЁзӨә SDA дёәиҫ“еҮәзҠ¶жҖҒпјҲеҚіж—¶пјүпјҢ第 3~4 иЎҢиЎЁзӨә C1 дёә 0 жӢүй«ҳSCLпјҢ C1 дёә 1/4 е‘Ёжңҹе°ұжӢүй«ҳгҖӮ第 5~6 иЎҢиЎЁзӨәпјҢ C1 дёә 0 жӢүдҪҺ SDAпјҢ C1 дёә 1/4 е‘Ёжңҹ + TR +TSU_STO е°ұжӢүй«ҳ SDAгҖӮ第 7~8 иЎҢиЎЁзӨәиҜҘжӯҘйӘӨжүҖйҖ—з•ҷзҡ„ж—¶й—ҙгҖӮ

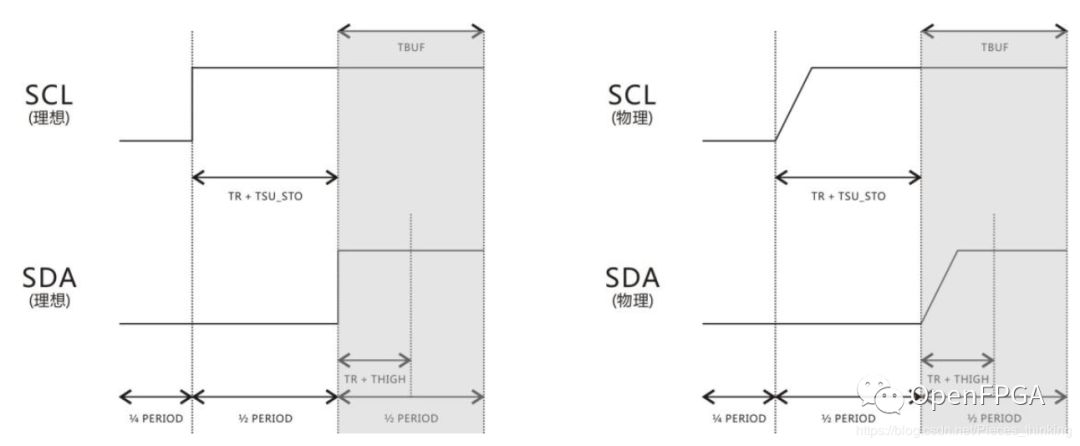

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғеӣҫ4 16 йҮҠж”ҫжҖ»зәҝ

вҖғвҖғжӯӨеӨ–пјҢз»“жқҹдҪҚиҝҳжңү Bus Free Time иҝҷдёӘж—¶еәҸеҸӮж•°пјҢIIC жҖ»зәҝеңЁй—ІзҪ®зҡ„зҠ¶жҖҒдёӢ SCL дёҺ SDAзӯүдҝЎеҸ·йғҪжҢҒз»ӯй«ҳз”өе№ігҖӮдё»жңәеҸ‘йҖҒз»“жқҹдҪҚд»ҘзӨәз»“жқҹж“ҚдҪңпјҢ然иҖҢдё»жңәжҢҒз»ӯжӢүй«ҳ SCL дҝЎеҸ·дёҺSDA дҝЎеҸ· TBUF д»ҘзӨәжҖ»зәҝйҮҠж”ҫгҖӮTBUF зҡ„жңүж•Ҳж—¶й—ҙд»Һ SCL дҝЎеҸ·дёҺ SDA дҝЎеҸ·жӢүй«ҳйӮЈдёҖеҲ»ејҖе§Ӣз®—иө·

вҖғвҖғж №жҚ®иЎЁ2 2 жүҖзӨәпјҢ TBUF жҳҜ 65 дёӘж—¶й’ҹпјҢз»“жһңеҰӮеӣҫ 16.6 жүҖзӨәпјҢ SDA дҝЎеҸ·жӢүй«ҳд№ӢеҗҺпјҢ SCLдёҺ SDA дҝЎеҸ·еҸӘиҰҒжҢҒз»ӯдҝқжҢҒ 1/2 е‘ЁжңҹпјҲеҚі 62 дёӘж—¶пјүпјҢеҹәжң¬дёҠе°ұиғҪж»Ўи¶і TBUFгҖӮеҰӮжһң笔иҖ…жҳҜдёҖдҪҚзҙ§еҜҶжҺ§ж—¶зӢӮдәәпјҢеҸҜиғҪж— жі•жҺҘеҸ—иҝҷж ·зҡ„з»“жһңпјҢеӣ дёәж»Ўи¶і TBUF е°‘дәҶ 3 дёӘж—¶й’ҹпјҢдёәжӯӨд»Јз Ғ2 3йңҖиҰҒжӣҙеҠЁдёҖдёӢпјҡ

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғ д»Јз Ғ 2 4 IICз»“жқҹдҪҚд»Јз Ғдҝ®ж”№

1. if( C1 == ( FQUARTER + FCLK + 3) -1 )

2. begin C1 <= 10'd0; i <= i + 1'b1; end

3. else C1 <= C1 + 1'b1;

вҖғвҖғеҰӮд»Јз Ғ 2 4жүҖзӨәпјҢ笔иҖ…дёә第 1 иЎҢеҶҷдёӢ +3 иЎЁзӨәиҜҘжӯҘйӘӨеӨҡйҖ—з•ҷ 3 дёӘж—¶й’ҹпјҢд»ҘиҮҙж»Ўи¶і TBUFгҖӮ

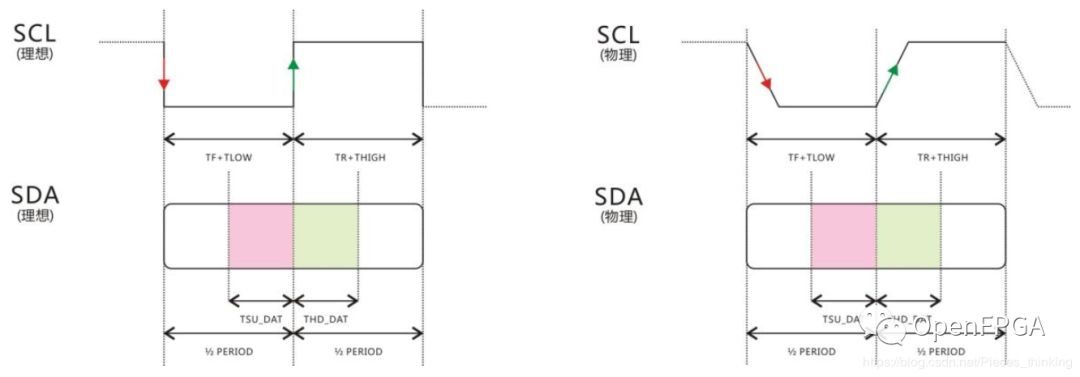

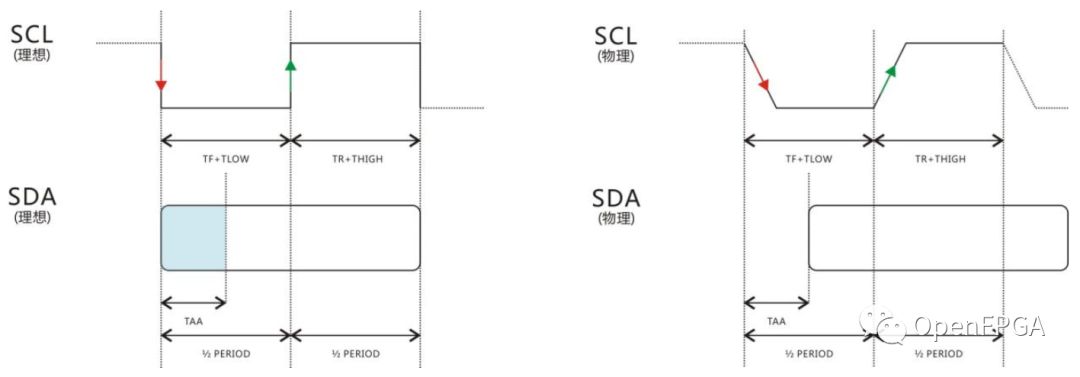

вҖғвҖғдёҚз®ЎеҜ№иұЎжҳҜи®ҫеӨҮең°еқҖпјҢж•°жҚ®ең°еқҖпјҢеҶҷе…Ҙж•°жҚ®пјҢиҜ»еҮәж•°жҚ®пјҢиҝҳжҳҜеә”зӯ”дҪҚпјҢеӨ§дјҷйғҪи§Ҷдёәж•°жҚ®дҪҚгҖӮIIC жҖ»зәҝзұ»дјје…¶д»–дј иҫ“еҚҸи®®пјҢе®ғжңүж—¶й’ҹдҝЎеҸ·д№ҹжңүдёҠеҚҮжІҝдёҺдёӢйҷҚжІҝгҖӮеҰӮеӣҫ 16.7 жүҖзӨәпјҢSCL дҝЎеҸ·зҡ„дёӢйҷҚжІҝеҜјиҮҙи®ҫеӨҮи®ҫзҪ®пјҲжӣҙж–°пјүж•°жҚ®пјҢдёҠеҚҮжІҝеҲҷжҳҜй”ҒеӯҳпјҲиҜ»еҸ–пјүж•°жҚ®гҖӮжңҹй—ҙпјҢTF+TLOW иЎЁзӨәж—¶й’ҹдҝЎеҸ·зҡ„еүҚеҚҠе‘ЁжңҹпјҢ TR+THIGH еҲҷиЎЁзӨәеҗҺеҚҠе‘ЁжңҹгҖӮжӯӨеӨ–пјҢдёәдәҶзЎ®дҝқж•°жҚ®жҲҗеҠҹжү“е…ҘеҜ„еӯҳеҷЁпјҢж•°жҚ®иў«дёҠеҚҮжІҝй”Ғеӯҳе“ӘдёҖеҲ»иө·пјҢ TSU_DAT иҝҳжңү THD_DAT еҝ…йЎ»еҫ—еҲ°ж»Ўи¶ігҖӮ

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғ еӣҫ2 17 ж•°жҚ®дҪҚжӣҙж–°жңүж•Ҳ

вҖғвҖғйҷӨжӯӨд№ӢеӨ–пјҢдёәдәҶзЎ®дҝқж•°жҚ®жңүж•Ҳиў«жӣҙж–°пјҢд№ҹеҝ…йЎ»зЎ®дҝқ TAA еҫ—еҲ°ж»Ўи¶іпјҢз»“жһңеҰӮеӣҫ2 17жүҖзӨәгҖӮзҗҶи§Је®ҢжҜ•д»ҘеҗҺпјҢе°ұеҸҜд»ҘејҖе§ӢеӯҰд№ пјҢеҶҷдёҖеӯ—иҠӮж•°жҚ®дёҺиҜ»дёҖеӯ—иҠӮж•°жҚ®пјҢиҝҳжңүеә”зӯ”дҪҚгҖӮ

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғеӣҫ2 18 еҶҷдёҖеӯ—иҠӮ

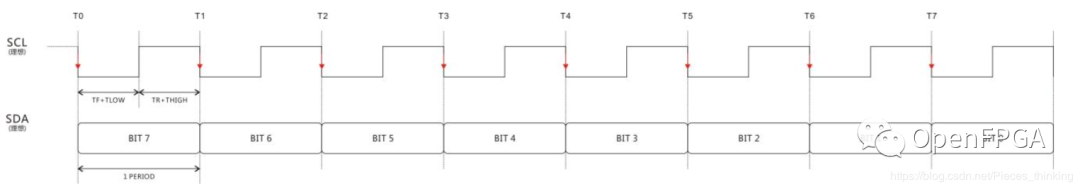

вҖғвҖғIIC жҖ»зәҝдёҖиҲ¬йғҪжҳҜдёҖдёӘеӯ—иҠӮдёҖдёӘеӯ—иҠӮиҜ»еҶҷж•°жҚ®пјҢеҰӮеӣҫ2 18 жүҖзӨәпјҢйӮЈжҳҜеҶҷдёҖеӯ—иҠӮзҡ„зҗҶжғіж—¶еәҸеӣҫпјҢдёҖеӯ—иҠӮж•°жҚ®жҳҜд»ҺжңҖй«ҳдҪҚејҖе§ӢеҶҷиө·гҖӮеҜ№жӯӨпјҢ Verilog еҸҜд»Ҙиҝҷж ·жҸҸиҝ°пјҢз»“жһңеҰӮд»Јз Ғ2 5жүҖзӨәпјҡ

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғд»Јз Ғ2 5 IIC жҖ»зәҝеҶҷдёҖдёӘеӯ—иҠӮ

1. 7,8,9,10,11,12,13,14:

2. begin

3. isQ = 1'b1;

4. rSDA <= D1[14-i];

5. if( C1 == 0 ) rSCL <= 1'b0;

6. else if( C1 == (TF + TLOW) ) rSCL <= 1'b1;

7. if( C1 == FCLK -1 ) begin C1 <= 10'd0; i <= i + 1'b1; end

8. else C1 <= C1 + 1'b1;

9. end

вҖғвҖғеҰӮд»Јз Ғ2 5 жүҖзӨәпјҢ第 1 иЎҢжңү 8 дёӘжӯҘйӘӨпјҢиЎЁзӨәеҶҷдёҖдёӘеӯ—иҠӮгҖӮ第 3 иЎҢ isQ дёә 1 иЎЁзӨә SDA дёәиҫ“еҮәзҠ¶жҖҒгҖӮ第 4 иЎҢиЎЁзӨәд»ҺжңҖй«ҳдҪҚејҖе§Ӣжӣҙж–° SDA зҡ„ж•°жҚ®дҪҚгҖӮ第 5~6 иЎҢиЎЁзӨәпјҢ C1 дёә 0 жӢүдҪҺSCLпјҢ C1 дёә TF+TLOW еҲҷжӢүй«ҳ SCLгҖӮ第 7~8 иЎҢиЎЁзӨәиҜҘжӯҘйӘӨйҖ—з•ҷдёҖдёӘе‘Ёжңҹзҡ„ж—¶й—ҙгҖӮ

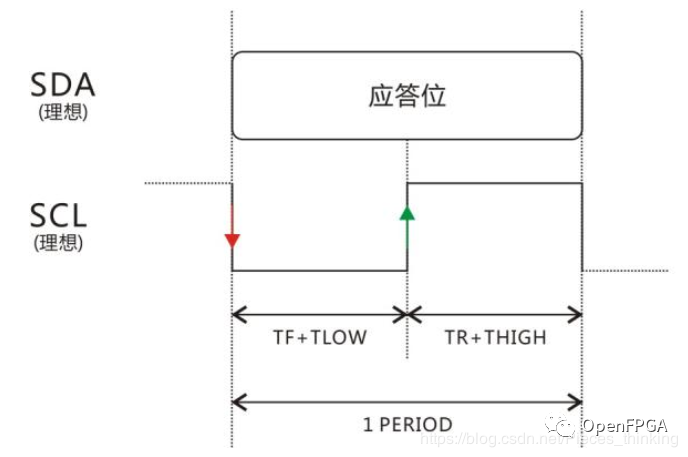

вҖғвҖғвҖғвҖғ вҖғеӣҫ2 19 еә”зӯ”дҪҚ

вҖғвҖғеә”зӯ”дҪҚжҳҜд»Һжңәз»ҷдәҲдё»жңәзҡ„еӣһзӯ”пјҢ 0 дёәжҳҜпјҢ1 дёәеҗҰгҖӮ然иҖҢпјҢд»Һж—Ғи§ӮзңӢпјҢиҜ»еҸ–еә”зӯ”дҪҚд№ҹжҳҜиҜ»еҸ–дёҖдҪҚж•°жҚ®дҪҚгҖӮеҪ“дё»жңәе®ҢжҲҗеҶҷе…ҘдёҖдёӘеӯ—иҠӮжҲ–иҖ…иҜ»еҸ–дёҖдёӘеӯ—иҠӮж•°жҚ®зҡ„ж—¶еҖҷпјҢд»ҺжңәйғҪдјҡдә§з”ҹеә”зӯ”дҪҚгҖӮдё»жңәжӢүдҪҺ SCL йӮЈеҲ»пјҢд»ҺжңәдҫҝдјҡеҸ‘йҖҒеә”зӯ”дҪҚпјҢ然еҗҺдё»жңәдјҡеҖҹз”ұдёҠеҚҮжІҝиҜ»еҸ–еә”зӯ”дҪҚгҖӮеҰӮеӣҫ2 19 жүҖзӨәпјҢдёҠеҚҮжІҝдјҡдә§з”ҹеңЁ TF + TLOW д№ӢеҗҺпјҢд№ҹжҳҜ 1/2 е‘ЁжңҹгҖӮеҜ№жӯӨпјҢ Verilog еҸҜд»Ҙиҝҷж ·иЎЁзӨәпјҢз»“жһңеҰӮд»Јз Ғ2 6жүҖзӨәпјҡ

вҖғвҖғвҖғ д»Јз Ғ2 6 IICеә”зӯ”дҪҚ

1. begin

2. isQ = 1'b0;

3.

4. if( C1 == FHALF ) isAck <= SDA;

5.

6. if( C1 == 0 ) rSCL <= 1'b0;

7. else if( C1 == FHALF ) rSCL <= 1'b1;

8.

9. if( C1 == FCLK -1 ) begin C1 <= 10'd0; i <= i + 1'b1; end

10. else C1 <= C1 + 1'b1;

11. end

вҖғвҖғеҰӮд»Јз Ғ2 6жүҖзӨәпјҢ第 2 иЎҢиЎЁзӨә SDA дёәиҫ“е…ҘзҠ¶жҖҒгҖӮ第 4~5 иЎҢиЎЁзӨәпјҢ C1 дёә 0 жӢүдҪҺ SCLпјҢC1 дёә 1/2 е‘ЁжңҹеҲҷжӢүй«ҳ SCLгҖӮ第 3 иЎҢиЎЁзӨәпјҢ C1 дёә 1/2 е‘Ёжңҹзҡ„ж—¶еҖҷиҜ»еҸ–еә”зӯ”дҪҚгҖӮ第 6~7 иЎҢиЎЁзӨәиҜҘжӯҘйӘӨйҖ—з•ҷ 1 дёӘе‘Ёжңҹзҡ„ж—¶й—ҙгҖӮ

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғ еӣҫ2 20 иҜ»дёҖеӯ—иҠӮ

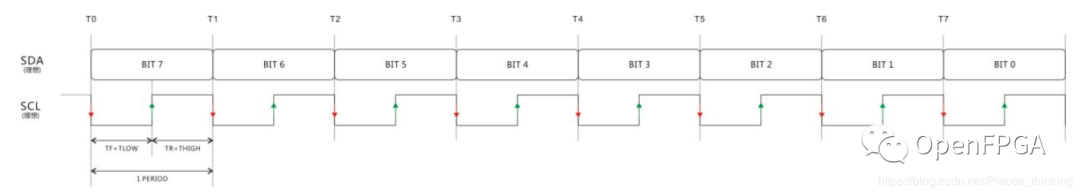

вҖғвҖғжүҖи°“иҜ»дёҖеӯ—иҠӮж•°жҚ®е°ұжҳҜйҮҚеӨҚиҜ»еҸ– 8 ж¬Ўеә”зӯ”дҪҚгҖӮеҰӮеӣҫ2 20жүҖзӨәпјҢ SCL зҡ„дёӢйҷҚжІҝеҜјиҮҙд»Һжңәжӣҙж–°ж•°жҚ®пјҢ然еҗҺдё»жңәеңЁ SCL зҡ„дёҠеҚҮжІҝиҜ»еҸ–ж•°жҚ®гҖӮжӯӨеӨ–пјҢд»Һжңәд№ҹдјҡз”ұй«ҳиҮідҪҺжӣҙж–°ж•°жҚ®дҪҚгҖӮиҮідәҺ Verilog еҲҷеҸҜд»Ҙиҝҷж ·иЎЁзӨәпјҢз»“жһңеҰӮд»Јз Ғ2 7жүҖзӨәпјҡ

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғд»Јз Ғ2 7 IICиҜ»дёҖеӯ—иҠӮ

1. 19,20,21,22,23,24,25,26: // Read

2. begin

3. isQ = 1'b0;

4. if( C1 == FHALF ) D1[26-i] <= SDA;

5.

6. if( C1 == 0 ) rSCL <= 1'b0;

7. else if( C1 == FHALF ) rSCL <= 1'b1;

8.

9. if( C1 == FCLK -1 ) begin C1 <= 10'd0; i <= i + 1'b1; end

10. else C1 <= C1 + 1'b1;

11. end

вҖғвҖғеҰӮд»Јз Ғ2 7жүҖзӨәпјҢ第 1 иЎҢиЎЁзӨәиҜ»еҸ–дёҖеӯ—иҠӮгҖӮ第 3 иЎҢиЎЁзӨә SDA дёәиҫ“е…ҘзҠ¶жҖҒпјҢ第 5~6 иЎҢиЎЁзӨәпјҢ C1 дёә 0 жӢүдҪҺ SCLпјҢ C1 дёә 1/2 е‘ЁжңҹеҲҷжӢүй«ҳ SCLгҖӮ第 4 иЎҢиЎЁзӨәпјҢ C1 дёә 1/2 е‘Ёжңҹзҡ„ж—¶еҖҷиҜ»еҸ–ж•°жҚ®пјҢиҖҢдё”ж•°жҚ®дҪҚз”ұй«ҳиҮідҪҺеӯҳе…Ҙ D1гҖӮ第 7~8 иЎҢиЎЁзӨәиҜҘжӯҘйӘӨйҖ—з•ҷдёҖдёӘе‘Ёжңҹзҡ„ж—¶й—ҙгҖӮ

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғ еӣҫ2 21 第дәҢж¬Ўиө·е§ӢдҪҚ

вҖғвҖғзҹҘйҒ“дё»жңәеҗ‘д»ҺжңәиҜ»еҸ–ж•°жҚ®зҡ„ж—¶еҖҷпјҢе®ғеҝ…йЎ»ж”№еҸҳи®ҫеӨҮең°еқҖзҡ„ж–№еҗ‘пјҢеӣ жӯӨиҜ»ж“ҚдҪңеҸҲ第дәҢж¬Ўиө·е§ӢдҪҚгҖӮеҰӮеӣҫ2 21жүҖзӨәпјҢж„ҹи§үдёҠ第дәҢж¬Ўиө·е§ӢдҪҚд№ҹжҳҜ第дёҖж¬Ўиө·е§ӢдҪҚпјҢдёҚиҝҮдёәдәҶдҝғдҪҝж”№еҸҳж–№еҗ‘жҲҗеҠҹпјҢ第дәҢж¬Ўиө·е§ӢдҪҚзӣёиҫғ第дёҖж¬Ўиө·е§ӢдҪҚзҡ„еүҚеҗҺйғҪжӢүдҪҺ 1/4 е‘ЁжңҹгҖӮеҜ№жӯӨпјҢ Verilog еҸҜд»Ҙиҝҷж ·иЎЁзӨәпјҢз»“жһңеҰӮд»Јз Ғ2 8жүҖзӨәпјҡ

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғд»Јз Ғ2 8 IIC第дәҢж¬Ўиө·е§ӢдҪҚ

1. begin

2. isQ = 1'b1;

3. if( C1 == 0 ) rSCL <= 1'b0;

4. else if( C1 == FQUARTER ) rSCL <= 1'b1;

5. else if( C1 == (FQUARTER + TR + TSU_STA + THD_STA + TF) ) rSCL <= 1'b0;

6.

7. if( C1 == 0 ) rSDA <= 1'b0;

8. else if( C1 == FQUARTER ) rSDA <= 1'b1;

9. else if( C1 == ( FQUARTER + TR + THIGH) ) rSDA <= 1'b0;

10.

11. if( C1 == (FQUARTER + FCLK + FQUARTER) -1 ) begin C1 <= 10'd0; i <= i + 1'b1; end

12. else C1 <= C1 + 1'b1;

13. end

вҖғвҖғеҰӮд»Јз Ғ2 8 жүҖзӨәпјҢ第 2 иЎҢиЎЁзӨә SDA дёәиҫ“еҮәзҠ¶жҖҒгҖӮ第 3~5 иЎҢиЎЁзӨәпјҢ C1 дёә 0 жӢүдҪҺ SCLпјҢC1 дёә 1/4 е‘ЁжңҹжӢүй«ҳ SCLпјҢ C1 дёә 1/4 е‘Ёжңҹ + TR + TSU_STA + THD_STA + TF дҫҝжӢүдҪҺSCLгҖӮ第 7~9 иЎҢиЎЁзӨәпјҢ C1 дёә 0 жӢүдҪҺ SDAпјҢ C1 дёә 1/4 е‘ЁжңҹжӢүй«ҳ SDAпјҢ C1 дёә 1/4 е‘Ёжңҹ + TR+ THIGH дҫҝжӢүдҪҺ SDAгҖӮ第 11~12 иЎҢиЎЁзӨәиҜҘжӯҘйӘӨеҒңз•ҷдёҖдёӘе‘Ёжңҹзҡ„ж—¶й—ҙгҖӮ

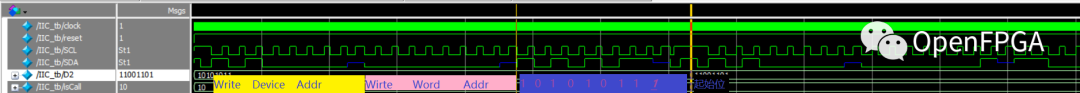

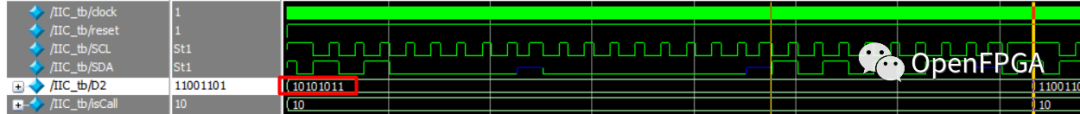

жҺҘдёӢжқҘжҳҜд»ҝзңҹйӘҢиҜҒпјҢз»“жһңеҰӮдёӢпјҡ

вҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғвҖғеӣҫ 2 22 IICжҖ»зәҝд»ҝзңҹж—¶еәҸеӣҫ

вҖғвҖғз»“еҗҲдёҠиҝ°д»ҝзңҹжіўеҪўеӣҫе’ҢзЁӢеәҸеҸҜд»ҘзңӢеҮәпјҡ

вҖғвҖғиө·е§ӢдҪҚпјҡSCLKдёәй«ҳз”өе№іж—¶пјҢSDATз”ұй«ҳеҲ°дҪҺпјҢжҢҮзӨәIICжҖ»зәҝдј иҫ“ж•°жҚ®зҡ„ејҖе§Ӣпјӣ

вҖғвҖғд№ӢеҗҺпјҢдј йҖҒдёҖдёӘеӯ—иҠӮзҡ„ж•°жҚ®пјҢеҚі4AпјҢдёәд»Һжңәзҡ„ең°еқҖпјҢйҡҸеҗҺпјҢи·ҹдәҶдёҖдёӘй«ҳз”өе№іпјҢдёәеә”зӯ”дҪҚпјӣ

вҖғвҖғд№ӢеҗҺпјҢдј йҖҒдёҖдёӘеӯ—иҠӮзҡ„ж•°жҚ®пјҢеҚі01пјҢдёәд»Һжңәең°еқҖзҡ„еӯҗең°еқҖпјҢйҡҸеҗҺпјҢи·ҹдәҶдёҖдёӘй«ҳз”өе№іпјҢдёәеә”зӯ”дҪҚпјӣ

вҖғвҖғд№ӢеҗҺпјҢдј йҖҒдёҖдёӘеӯ—иҠӮзҡ„ж•°жҚ®пјҢеҚі08пјҢдёәдёҠйқўеӯҗең°еқҖеҜ„еӯҳеҷЁй…ҚзҪ®зҡ„ж•°жҚ®пјҢйҡҸеҗҺпјҢи·ҹдәҶдёҖдёӘй«ҳз”өе№іпјҢдёәеә”зӯ”дҪҚпјӣ

вҖғвҖғжңҖеҗҺпјҢдёәеҒңжӯўдҪҚпјҢSCLKдёәй«ҳз”өе№іж—¶пјҢSDATз”ұдҪҺеҲ°й«ҳпјҢжҢҮзӨәиҜҘж¬ЎIICжҖ»зәҝдј иҫ“ж•°жҚ®зҡ„з»“жқҹгҖӮ

вҖғвҖғз”ұд»ҝзңҹз»“жһңеҸҜзҹҘпјҢеҪ“дј йҖҒе®ҢдёҖдёӘеӯ—иҠӮеҗҺпјҢSDATдёәдёҖдёӘи„үеҶІзҡ„й«ҳз”өе№іпјҢиҖҢдёҚжҳҜд»ҺеҷЁд»¶е…Ҳе°ҶSDATжӢүдҪҺеҶҚжӢүй«ҳпјҢиҝҷж ·д№ҹжҳҜеҸҜд»Ҙзҡ„гҖӮ

д»ҘдёҠе°ұжҳҜжҖҺд№ҲиҝӣиЎҢIICеҚҸи®®зҡ„FPGAе®һзҺ°пјҢе°Ҹзј–зӣёдҝЎжңүйғЁеҲҶзҹҘиҜҶзӮ№еҸҜиғҪжҳҜжҲ‘们ж—Ҙеёёе·ҘдҪңдјҡи§ҒеҲ°жҲ–з”ЁеҲ°зҡ„гҖӮеёҢжңӣдҪ иғҪйҖҡиҝҮиҝҷзҜҮж–Үз« еӯҰеҲ°жӣҙеӨҡзҹҘиҜҶгҖӮжӣҙеӨҡиҜҰжғ…敬иҜ·е…іжіЁдәҝйҖҹдә‘иЎҢдёҡиө„и®Ҝйў‘йҒ“гҖӮ

е…ҚиҙЈеЈ°жҳҺпјҡжң¬з«ҷеҸ‘еёғзҡ„еҶ…е®№пјҲеӣҫзүҮгҖҒи§Ҷйў‘е’Ңж–Үеӯ—пјүд»ҘеҺҹеҲӣгҖҒиҪ¬иҪҪе’ҢеҲҶдә«дёәдё»пјҢж–Үз« и§ӮзӮ№дёҚд»ЈиЎЁжң¬зҪ‘з«ҷз«ӢеңәпјҢеҰӮжһңж¶үеҸҠдҫөжқғиҜ·иҒ”зі»з«ҷй•ҝйӮ®з®ұпјҡis@yisu.comиҝӣиЎҢдёҫжҠҘпјҢ并жҸҗдҫӣзӣёе…іиҜҒжҚ®пјҢдёҖз»ҸжҹҘе®һпјҢе°Ҷз«ӢеҲ»еҲ йҷӨж¶үе«ҢдҫөжқғеҶ…е®№гҖӮ