Vivado中IP是如何控制端口的可见与不可见,相信很多没有经验的人对此束手无策,为此本文总结了问题出现的原因和解决方法,通过这篇文章希望你能解决这个问题。

测试平台Vivado 2017.2

一、建立一个简单的AXI IP

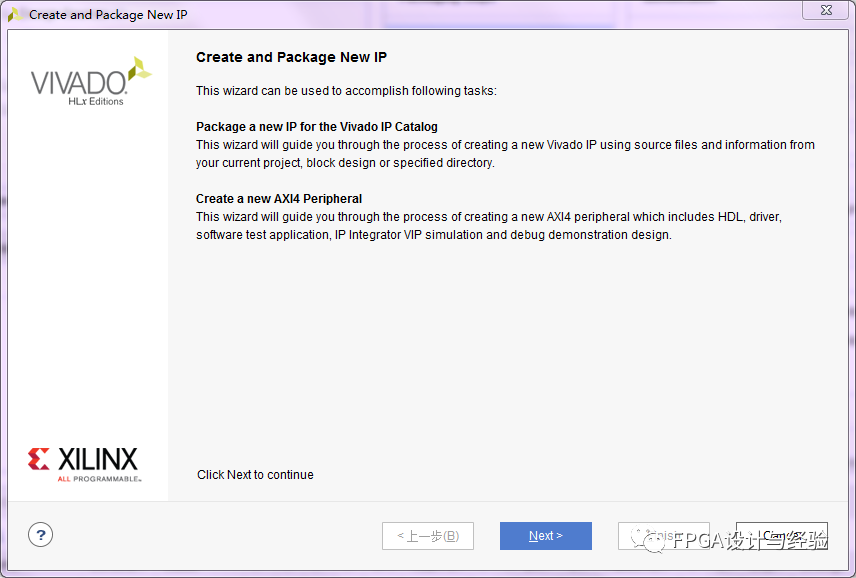

最简单的封装IP莫过于使用Vivado的Tools菜单下(已有工程打开),Create And Package New IP子项建立:

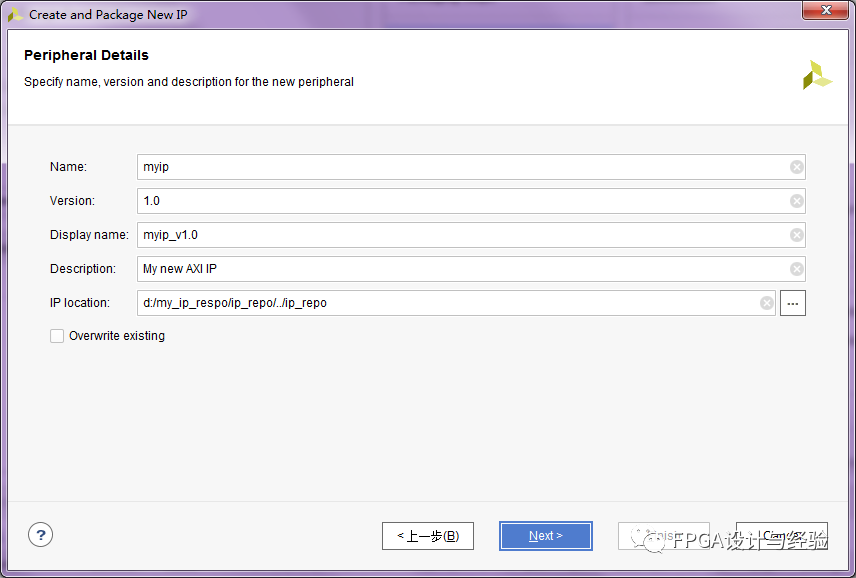

这是配置AXI4 IP的名字、版本等信息,版本、显示名字和描述在后面可以修改,根据需要填写。

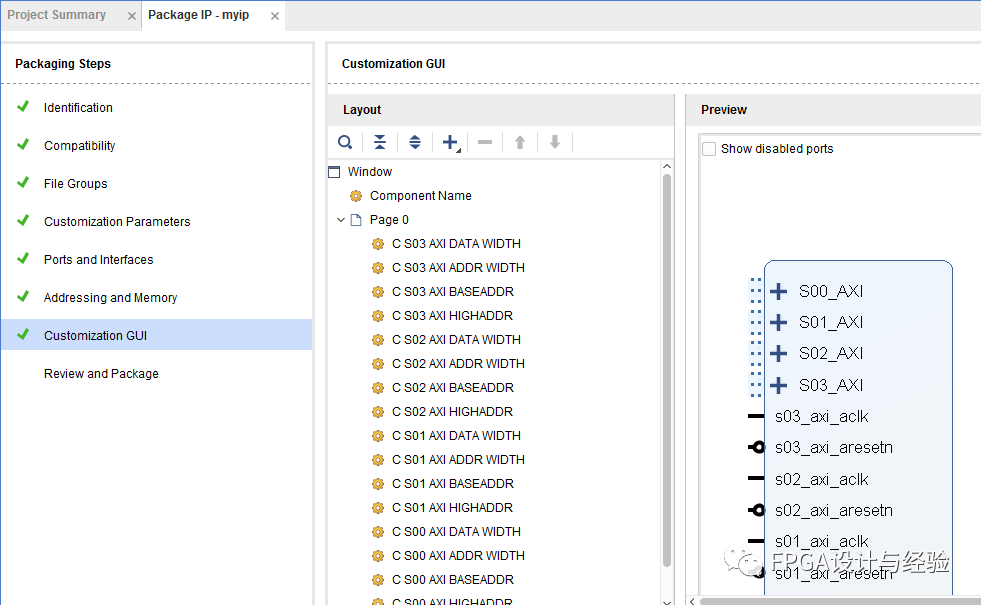

这个是AXI4 IP的配置界面,接口类型提供了Lite、Full和Stream三种可选,此处我添加4个Slave的Lite接口。

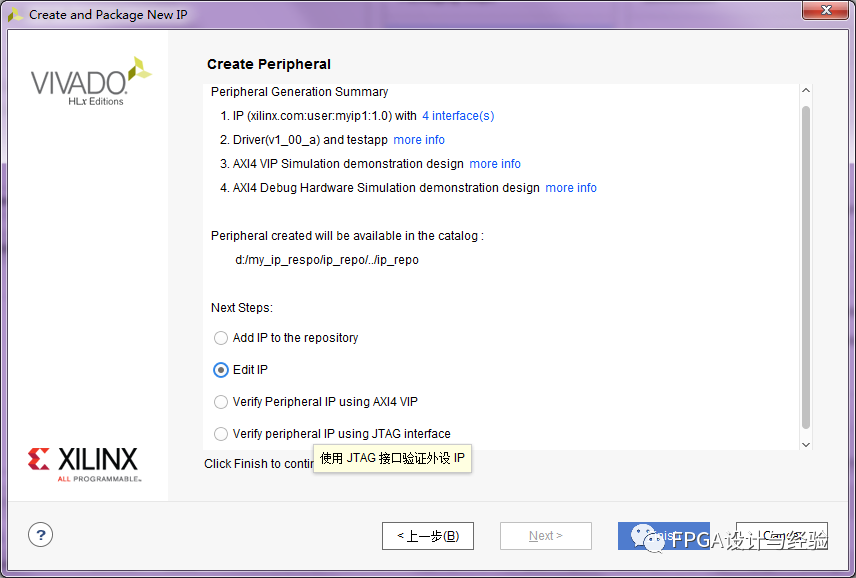

最后点击Finish就完成IP创建,由于我需要对代码进行修改,我选择Edit IP,除此之外还有Verify Peripheral IP using AXI VIP和Verify peripheral IP using JTAG interface是两种不同的验证手段, VIP其实就是Altera的Virtual JTAG,而后者是Vivado内带了一个叫Debug Bridge的IP,它可以实现AXI操作JTAG的功能,实现FPGA控制另一块FPGA通过JTAG口,还有一个叫JTAG to AXI master的IP正好反过来,是JTAG控制AXI。

二、如何控制IP端口可配置显示

在IP设计时,最为头疼的是如果我的IP共有40个对外的Port,而我并不需要40个对外的Port总是需要配置连线,我可能只需要20Port。通过配置Parameter可以使其他的20个Port不可见,Vivado提供了这种功能,它就是Enablement Expression功能,它有三个作用:

1.它可以启用或禁用一些端口或BUS

2.它可以启用或禁用自定义的parameter;

3.它可以计算自定义的parameter的值。

本文仅对端口/BUS的启用与禁用进行说明:

打开IP的编辑界面,切换到Ports and Interface选项卡:

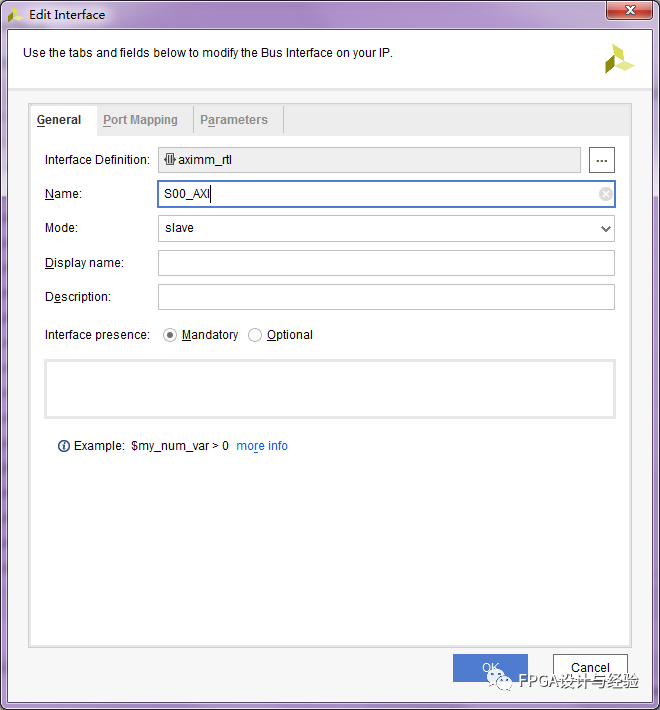

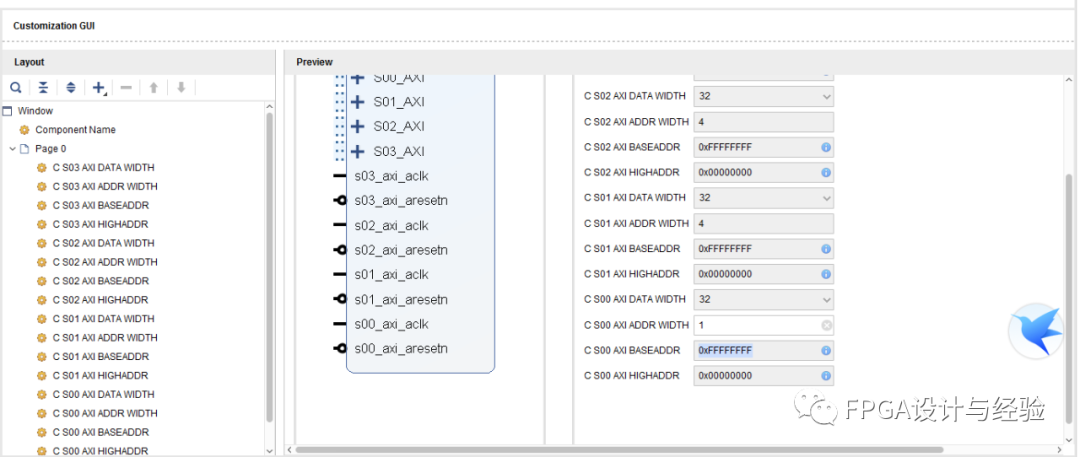

需要将Interface presence项从Mandatory选中切换为Optional选中,在Interface presence下面编辑框填写$C_S00_AXI_ADDR_WIDTH != 0,这是tcl语法,变量引用需要在变量名前添加$符号,点击OK:

右键C S00 AXI ADDR WIDTH选择Edit Parameter;

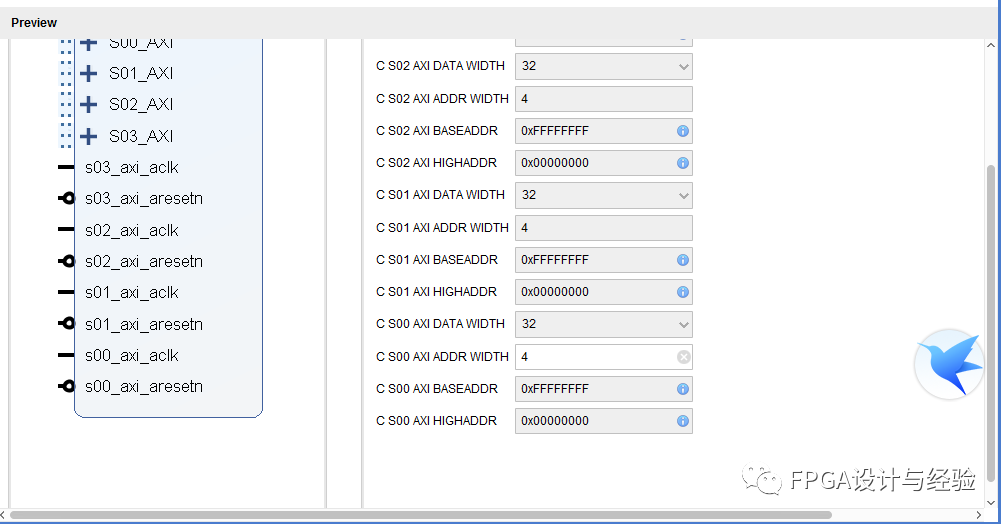

目光转到Preview界面,可以发现C S00 AXI ADDR WIDTH对应的文本编辑框不再处于灰色不可以编辑状态,修改值为0,然后点击其他的文本框使之设置值生效。

发现S00_AXI又神奇的出现了,这就是总线的禁用,端口的禁用是类似的。

看完上述内容,你们掌握Vivado中IP是如何控制端口的可见与不可见的方法了吗?如果还想学到更多技能或想了解更多相关内容,欢迎关注亿速云行业资讯频道,感谢各位的阅读!

亿速云「云服务器」,即开即用、新一代英特尔至强铂金CPU、三副本存储NVMe SSD云盘,价格低至29元/月。点击查看>>

免责声明:本站发布的内容(图片、视频和文字)以原创、转载和分享为主,文章观点不代表本网站立场,如果涉及侵权请联系站长邮箱:is@yisu.com进行举报,并提供相关证据,一经查实,将立刻删除涉嫌侵权内容。

原文链接:https://my.oschina.net/algebra/blog/4341202