这篇文章主要讲解了“Linux中的Makefile怎么用”,文中的讲解内容简单清晰,易于学习与理解,下面请大家跟着小编的思路慢慢深入,一起来研究和学习“Linux中的Makefile怎么用”吧!

简而言之makefile的作用就是“自动编译”,当我们将整个项目的Makefile都写完之后,只需要一个简单的make命令,就可以实现自动编译了。

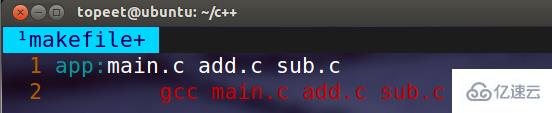

makefile

Makefile

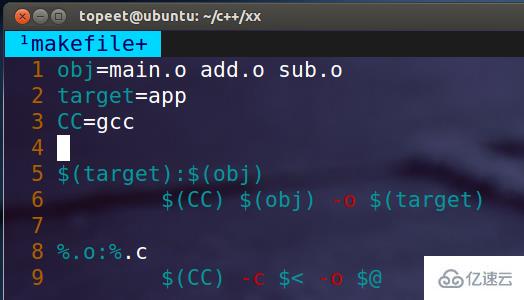

规则的三个要素:目标、依赖、命令

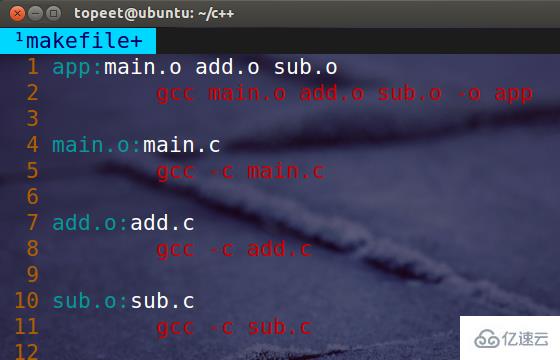

makefile可以有多个规则,当第一个规则的的命令在执行的时候发现没有相应的依赖,就在下面的规则中找。最上面的规则的目标是终极目标一定写在最上面,也就是最后要生成的文件。

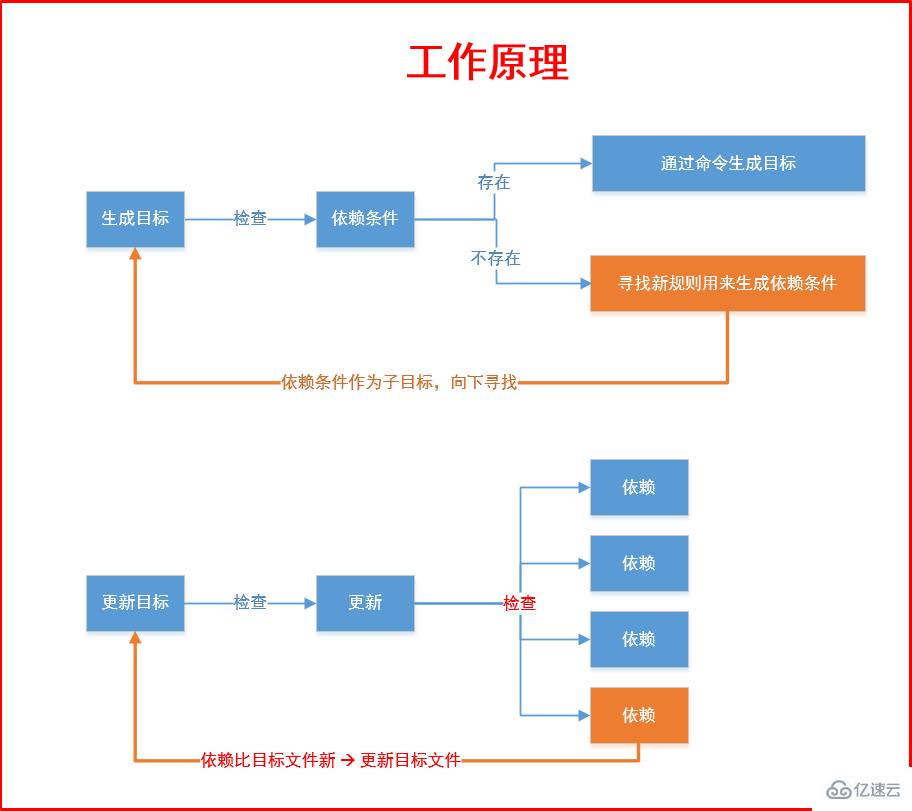

多文件Makefile的更新原理(基于时间)

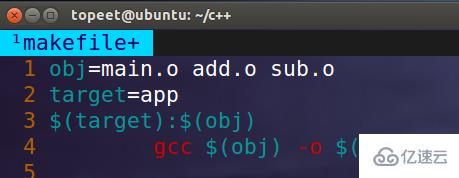

自定义变量

obj=main.o add.o sub.o

引用的时候直接使用 $(obj)

自动变量()

$

$@:规则中的目标

$^: 规则中所有的依赖

模式自动匹配 %

子规则中::

makefile维护的变量(通常大写,自己可以修改)

CC:cc(即gcc)

APPFLAGS:预处理使用的选项

CFLAGS:编译的时候使用的选项

LDFLAGS:链接库使用的选项

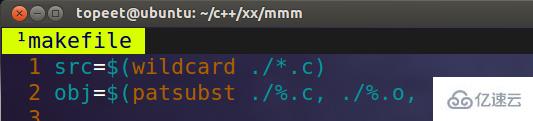

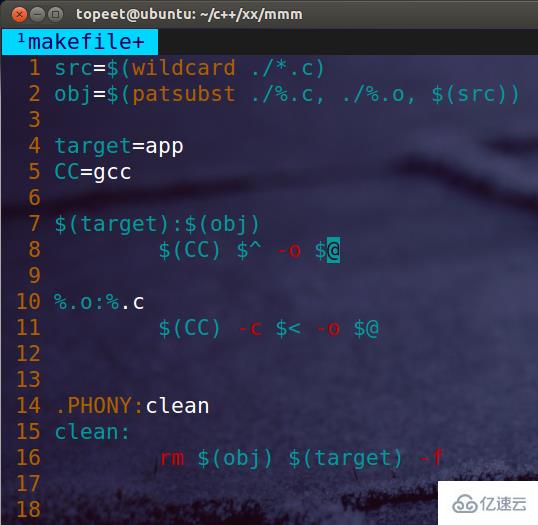

wildcard 查找当前目录下所有.c文件,返回值给src

src=$(wildcard ./*.c)

patsubst 替换所有.c文件为.o文件

obj=$(patsubst ./%.c, ./%.o, $(src))

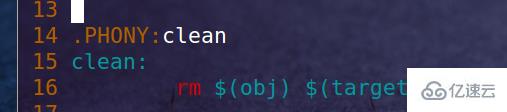

在makefile最后加入clean的目标,为了重新编译所有文件得删除原来生成的文件

感谢各位的阅读,以上就是“Linux中的Makefile怎么用”的内容了,经过本文的学习后,相信大家对Linux中的Makefile怎么用这一问题有了更深刻的体会,具体使用情况还需要大家实践验证。这里是亿速云,小编将为大家推送更多相关知识点的文章,欢迎关注!

免责声明:本站发布的内容(图片、视频和文字)以原创、转载和分享为主,文章观点不代表本网站立场,如果涉及侵权请联系站长邮箱:is@yisu.com进行举报,并提供相关证据,一经查实,将立刻删除涉嫌侵权内容。