Xilinx中的Primitives和Macros该怎么理解,针对这个问题,这篇文章详细介绍了相对应的分析和解答,希望可以帮助更多想解决这个问题的小伙伴找到更简单易行的方法。

源语(Primitives)-Xilinx库中最简单的设计元素。Primitives 基元是设计元素“原子”。Xilinx原语的示例包括简单缓冲区BUF和带有时钟使能和清除功能的D触发器FDCE。

宏(Macros)-Xilinx库的设计元素“分子”。可以从设计元素原语或宏创建宏。例如,FD4CE触发器宏是4个FDCE原语的组合。

Xilinx的原语分为10类,包括:计算组件,IO端口组件,寄存器/锁存器,时钟组件,处理器组件,移位寄存器,配置和检测组件,RAM/ROM组件,Slice/CLB组件,G-tranceiver。具体原语资源更详尽描述请参考文档UG799以及UG768。

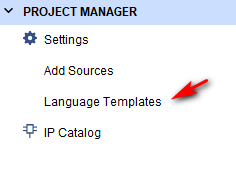

1>打开PROJECT MANAGER-->Language Templates

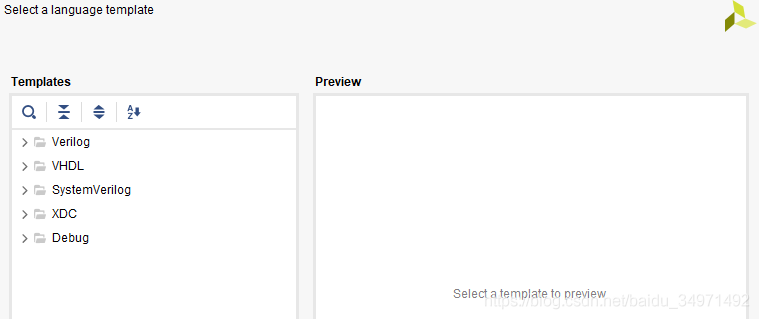

2>语言模板如下图5大部分

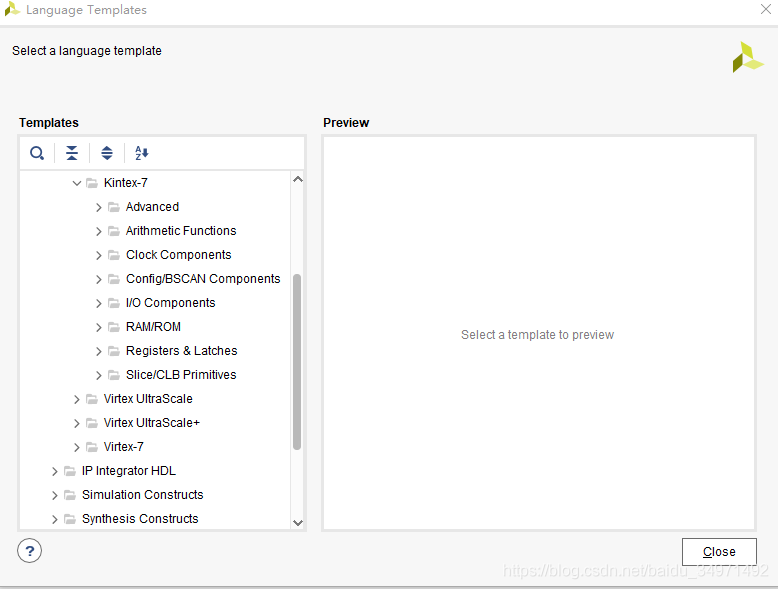

3>选择相应的器件类型和模块组件。

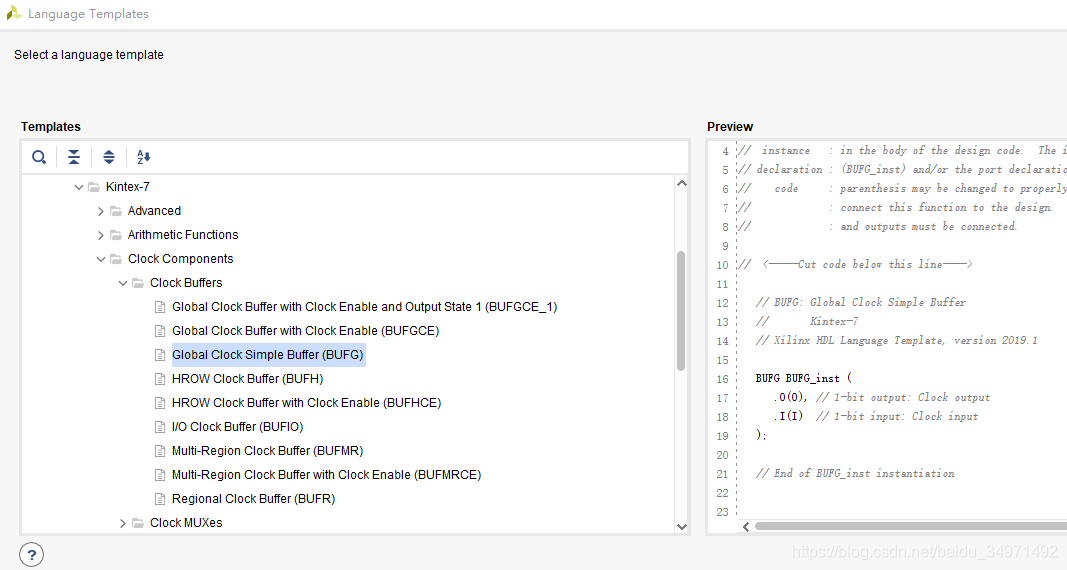

4>BUFG示例

// BUFG : In order to incorporate this function into the design,// Verilog : the following instance declaration needs to be placed// instance : in the body of the design code. The instance name// declaration : (BUFG_inst) and/or the port declarations within the// code : parenthesis may be changed to properly reference and// : connect this function to the design. All inputs// : and outputs must be connected.// <-----Cut code below this line----> // BUFG: Global Clock Simple Buffer // Kintex-7 // Xilinx HDL Language Template, version 2019.1 BUFG BUFG_inst ( .O(O), // 1-bit output: Clock output .I(I) // 1-bit input: Clock input ); // End of BUFG_inst instantiationPrimitive: Global Clock Simple Buffer

介绍:

该设计元素是一个高扇出缓冲器,可将信号连接到全局路由资源,以实现信号的低偏斜分布。BUFG通常用于时钟网络以及其他高扇出网络,如置位/复位和时钟使能。

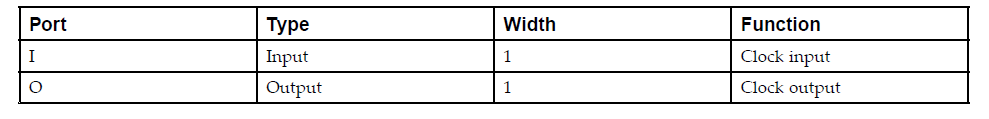

端口描述:

关于Xilinx中的Primitives和Macros该怎么理解问题的解答就分享到这里了,希望以上内容可以对大家有一定的帮助,如果你还有很多疑惑没有解开,可以关注亿速云行业资讯频道了解更多相关知识。

亿速云「云服务器」,即开即用、新一代英特尔至强铂金CPU、三副本存储NVMe SSD云盘,价格低至29元/月。点击查看>>

免责声明:本站发布的内容(图片、视频和文字)以原创、转载和分享为主,文章观点不代表本网站立场,如果涉及侵权请联系站长邮箱:is@yisu.com进行举报,并提供相关证据,一经查实,将立刻删除涉嫌侵权内容。

原文链接:https://my.oschina.net/u/4579395/blog/4959340